# Role of Photolithographic Process in Semiconductor Manufacturing

# Dr. Avinash M. Pawar

Ph.D. Mechanical Engineering, Bharati Vidyapeeth's College of Engineering for Women, Pune avinash.m.pawar@bharatividyapeeth.edu

### Article History

Article Submission 04 October 2021 Revised Submission 11 November 2021 Article Accepted 10 December 2021 Article Published 20 January 2022

#### Abstract

Semiconductor Fabrication is a business of high capital speculation and quick evolving nature. To be serious, the creation in a fabrication should be viably arranged and planned beginning from the inclining up stage, with the goal that the business objectives, for example, on-time conveyance, high yield volume and viable utilization of capital concentrated hardware can be accomplished. Reproduction gives a successful tool to characterizing the way from serious ideas to true arrangements. More consideration is presently being centred on the precision of information gathered, implies for separating and bringing in information to the models, and staying up to date with changes in the fabrication. The directors and architects are these days properly worried about whether the model is a decent portrayal of the fabrication, and whether the outcomes are right. This is tended to through check and approval. The re-enactment group does approval by looking at the spreadsheet models and fabrication information, however formal systems have not been applied with the end goal of approval. The check and approval techniques are not officially recorded either. Additionally, the administration chose to explore different avenues regarding new programming called Lucent AP.

# I. Introduction

The dissemination resistors that were examined comprise of a resistor assortment of un-cut silicon zone at the two lateral positions of the die, which is produced using silicon cut methodology. Un-cut silicon was fixed for the resistor manufacture process because of extraordinary sheet negligible resistance of 50 ohms. The top view of resistor is allotted as contacts for metallization.

Keywords: Semiconductor Fabrication, ASIC, Lucent AP tool

This region is cut to accomplish low leakage impedance. The top notch of resistor is more extensive compared to that of circumference of the resistor. Primary Care to be rendered to design resistor pair that has indistinguishable associations on the metal level. During the wafer fabrication process, the parcels experience the photograph procedure a few times. Each time requires an alternate example and after every photograph step different procedure, for example, embeds or plasma engraving will happen.

The model Includes work and its accessibility with shifts. Note that this fabrication is in the inclining stage and the model was worked for a specific period in the slope. The model must be refreshed, i.e., the routings, gear and work ought to be included as the progressions happen in the fabrication. This model is utilized to contemplate the effect of the working strategies on the process durations, throughput, WIP (work in process) levels, line times, and usages of the photograph zone. The photograph region is relied upon to be the bottleneck since every wafer experiences it on various occasions.

6 © IJNPME 2022

ISSN: 2250-0839

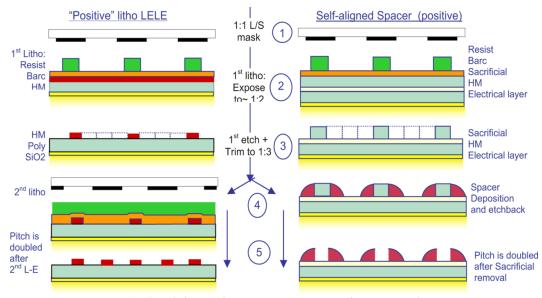

Figure 1: Photolithographic Process in Semiconductor Manufacturing

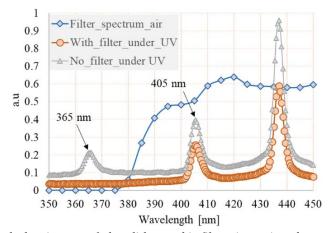

Figure 2: Graph showing use of photolithographic filters in semiconductor manufacturing

Estimations were done using a motorized Cascade Micro-tech test station and a 4156-A semiconductor limit analyser from Agilent Technologies. The six test needles are required to play out the four-wire estimations on each resistor pair. Contact is made to every one of the six pads, by then the estimation units of the 4156-arc set up to such a degree, that underlying one resistor is assessed twice, with no alteration in the plan between the first and the resulting estimation. They are basically done by repeating the estimation method on the limit analyser. A brief timeframe later, the ensuing resistor is assessed twice. The perplex of each pair is then the differentiation of the two restriction estimations of the key estimation. The resulting estimation is used to check the repeatability of the estimation course of action. After all individual resistor sets are evaluated; the standard deviation of the restriction differentiation is resolved and plotted against the deterrent regard.

Fig 3: photolithographic process in semiconductor manufacturing

ISSN: 2250-0839 © IJNPME 2022

# References

- S. J. Pearton et al., "Ion implantation for creating room temperature ferromagnetism in wide bandgap semiconductors," 2003 International Symposium on Compound Semiconductors, San Diego, CA, USA, 2003, pp. 110-111, doi: 10.1109/ISCS.2003.1239930.

- Z. C. Feng, E. Armour, A. G. Thompson and R. A. Stall, "Whole wafer characterization of large size [2] GaAs-AlGaAs semiconductor materials prepared by MOCVD TurboDisc/sup TM/ technology," Compound Semiconductors 1997. Proceedings of the IEEE Twenty-Fourth International Symposium Compound Semiconductors, San Diego, CA, USA, 1997, 287-290, 10.1109/ISCS.1998.711637.

- J. Ke Kian Seng, "Development of 3-dimensional visualization of semiconductor testing," 2004 IEEE [3] International Conference on Semiconductor Electronics, Kuala Lumpur, 2004, pp. 4 pp.-, doi: 10.1109/SMELEC.2004.1620866.

8 © IJNPME 2022

ISSN: 2250-0839